Scheduling Toolbox

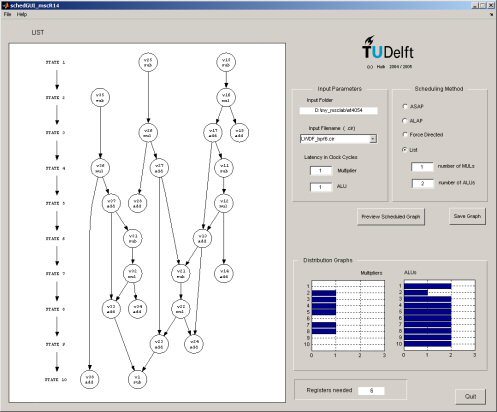

The Scheduling Toolbox consists of a set of MATLAB functions and a GUI which eases visualization of the scheduling methods. Input is a text file in a proprietary format describing a circuit or a mathematical function. The final output is a set of MATLAB and (synthesizable) VHDL files and testbenches.

These toolbox functions have primarily been written to enlighten lectures about scheduling algorithms and are therefore set up the way they are. This means that here and there flexibility may be less than could be desired. However, since the toolbox itself generates MATLAB and VHDL files, these can be tailored at will.

Computations are performed using a user definable fixed-point format and can be extensively tested in the MATLAB environment.

The results can be used as a reference for the VHDL simulations which should show a bit-true conformity with the MATLAB output.

VHDL output is at RTL level and is based on a (time-scheduled) combination of ALUs, MULtipliers, REGisters and multiplexers.

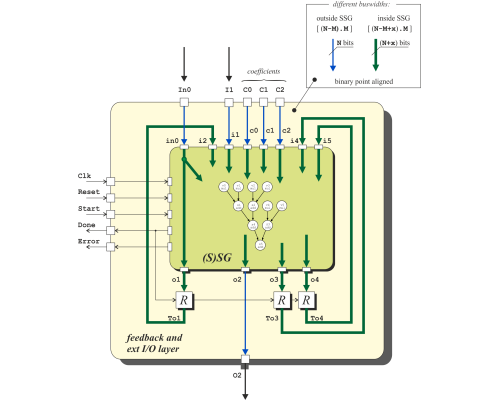

The lowest level architecture implements the actual "Scheduled Sequencing Graph (SSG)" for the chosen scheduling method.

A higher level architecture connects this SSG to input and outputs of the circuit and a.o. defines delay elements if present.

Setup of the SSG

Example of a Scheduled Sequencing Graph:

Screenshot of schedGUI

The Toolbox has been tested with the following software:

- MATLAB Release 14 (Sp2),

- ModelSim SE (6.0),

- Synplify Pro (8.0) and

- Xilinx ISE (7.1i)

for interfacing to an AVR-core on an AVNET Spartan-3 Development Kit with an XC3S2000.

The numbers between the parenthesis are the version numbers that were installed at the time of writing (not unnecessarily the latest versions).

For drawing the graphs, part of the Graphviz (Graph Visualization Software) package has been used. See http://www.graphviz.org/

| February 10, 2006 |